Marco Ghibaudi

20 Jun 2023

The race is on to make quantum computers useful, sooner than previously imaginable. It’s a massive undertaking where many different types of technology must be designed, built and then engineered to work together across an integrated quantum stack.

Modern quantum computers are a hybrid of the same classical computing hardware that powers high performance computers (HPC) plus a quantum processing unit (QPU) utilising the qubits that give a quantum computer its superpowers. The classical interface, essentially, instructs the QPU with a continuous stream of instructions to perform the operations that keep the QPU up and running.

The QPU is connected to the classical interface using a limited, fixed number of wires, so there’s a bandwidth problem between these classical and quantum systems. As we scale up quantum computers to the tens, hundreds and then thousands of qubits to unlock the true potential of quantum computing, the situation gets worse.

Qubits are also delicate and highly susceptible to a high volume of data errors due to external interference (‘noise’). This noise renders them useless unless we carefully control them and their surrounding environment. One way to minimise noise for most types of qubits is to artificially keep the QPU at extremely low temperatures – often a few millikelvin above absolute zero.

Our invention provides the high bandwidth rates required as quantum computers scale while minimising the huge power demands imposed by such extreme refrigeration requirements.

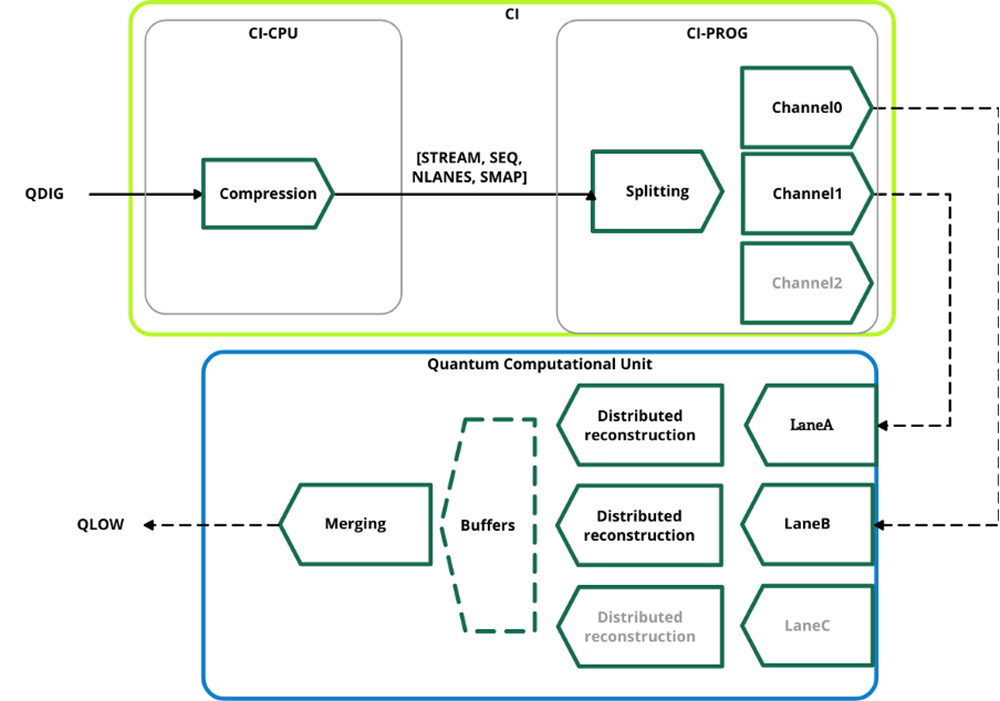

The patent covers our method for transmitting control signals from a classical computing interface to a QPU. The method involves compressing digital control signals at the classical interface and splitting the compressed control signals into sub-streams. The sub-streams are then transmitted to the QPU in a staggered configuration.

As set out in the patent, this method “allows control signals to be transmitted to the QPU in a way that respects power constraints and minimises error rates, which in turn facilitates the development of scalable fault-tolerant universal quantum computers with thousands or more physical qubits”.

This staggered configuration used to transmit sub-streams also “allows for crosstalk to be reduced on communication channels between the classical interface and the QPU, thereby reducing error rates and power consumption”.